EPFL researchers have combined low-power chip design, machine learning algorithms, and soft implantable electrodes to produce a neural interface that can identify and suppress symptoms of various neurological disorders.

Mahsa Shoaran of the Integrated Neurotechnologies Laboratory in the School of Engineering collaborated with Stéphanie Lacour in the Laboratory for Soft Bioelectronic Interfaces to develop NeuralTree: a closed-loop neuromodulation system-on-chip that can detect and alleviate disease symptoms.

Thanks to a 256-channel high-resolution sensing array and an energy-efficient machine learning processor, the system can extract and classify a broad set of biomarkers from real patient data and animal models of disease in-vivo, leading to a high degree of accuracy in symptom prediction.

“NeuralTree benefits from the accuracy of a neural network and the hardware efficiency of a decision tree algorithm,” Shoaran says. “It’s the first time we’ve been able to integrate such a complex, yet energy-efficient neural interface for binary classification tasks, such as seizure or tremor detection, as well as multi-class tasks such as finger movement classification for neuroprosthetic applications.”

Their results were presented at the 2022 IEEE International Solid-State Circuits Conference and published in the IEEE Journal of Solid-State Circuits.

Efficiency, scalability, and versatility

NeuralTree functions by extracting neural biomarkers—patterns of electrical signals known to be associated with certain neurological disorders—from brain waves. It then classifies the signals and indicates whether they herald an impending epileptic seizure or Parkinsonian tremor, for example. If a symptom is detected, a neurostimulator—also located on the chip—is activated, sending an electrical pulse to block it.

Shoaran explains that NeuralTree’s unique design gives the system an unprecedented degree of efficiency and versatility compared to the state-of-the-art. The chip boasts 256 input channels, compared to 32 for previous machine-learning-embedded devices, allowing more high-resolution data to be processed on the implant.

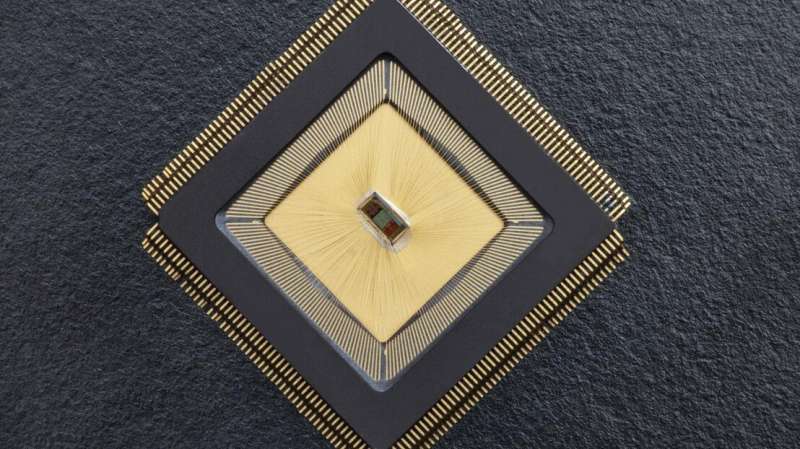

The chip’s area-efficient design means that it is also extremely small (3.48mm2), giving it great potential for scalability to more channels. The integration of an “energy-aware” learning algorithm—which penalizes features that consume a lot of power—also makes NeuralTree highly energy efficient.

In addition to these advantages, the system can detect a broader range of symptoms than other devices, which until now have focused primarily on epileptic seizure detection. The chip’s machine learning algorithm was trained on datasets from both epilepsy and Parkinson’s disease patients, and accurately classified pre-recorded neural signals from both categories.

“To the best of our knowledge, this is the first demonstration of Parkinsonian tremor detection with an on-chip classifier,” Shoaran says.

Self-updating algorithms

Shoaran is passionate about making neural interfaces more intelligent to enable more effective disease control, and she is already looking ahead to further innovations.

“Eventually, we can use neural interfaces for many different disorders, and we need algorithmic ideas and advances in chip design to make this happen. This work is very interdisciplinary, and so it also requires collaborating with labs like the Laboratory for Soft Bioelectronic Interfaces, which can develop state-of-the-art neural electrodes, or labs with access to high-quality patient data.”

As a next step, she is interested in enabling on-chip algorithmic updates to keep up with the evolution of neural signals.

“Neural signals change, and so over time the performance of a neural interface will decline. We are always trying to make algorithms more accurate and reliable, and one way to do that would be to enable on-chip updates, or algorithms that can update themselves.”

More information:

Uisub Shin et al, NeuralTree: A 256-Channel 0.227-μJ/Class Versatile Neural Activity Classification and Closed-Loop Neuromodulation SoC, IEEE Journal of Solid-State Circuits (2022). DOI: 10.1109/JSSC.2022.3204508

Uisub Shin et al, A 256-Channel 0.227µJ/class Versatile Brain Activity Classification and Closed-Loop Neuromodulation SoC with 0.004mm2-1.51 µW/channel Fast-Settling Highly Multiplexed Mixed-Signal Front-End, 2022 IEEE International Solid- State Circuits Conference (ISSCC) (2022). DOI: 10.1109/ISSCC42614.2022.9731776

Journal information:

IEEE Journal of Solid-State Circuits

Source: Read Full Article